同社開発陣と野村ケンジ氏のトークセッションも実施

【ポタ研】デノン、USB-DAC内蔵ポタアン「DA-10」発表会を開催 - 設計担当が開発秘話を語る

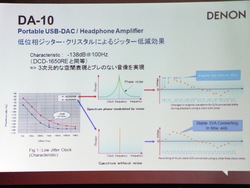

■ジッターを徹底排除するMaster Clock Design

デジタル部のもうひとつの大きな特徴といえる「DAC Master Clock Design」にも話は及んだ。DA-10はDACをマスターとして周辺回路にクロックを供給することで、デジタル回路の高精度な同期を実現する。そして、DACに供給するクロックの精度を最優先するために、DAC近傍にクロックモジュールを配置しているのだ。

「マスタークロックの置く場所をDACの近傍とした理由は、各デジタル部の中でも特にDACが、精度の高いマスタークロックを必要としているからです。どれだけ高性能なDACでも動作する基準はクロックです。ですから高品位なクロックを用意してあげれば、そのDACの最高のパフォーマスが得られます。そのために、DACの近傍にクロックを配置しているのです」(出口氏)

また、44.1kHz系と48kHz系で2系統のクロックを用意している点についても説明してくれた。「なぜクロックが2つあるのかというと、44.1kHz系のクロックで48kHz系に合わせようとしても定数倍にならないので、忠実なクロック生成が難しく、時間軸上の揺らぎ(ジッター)が出やすくなってしまいます。ジッターは音質にもろに影響してまうので、クロックを2系統配置して音源ごとに純度の高いクロックを提供してジッターを防いでいるのです」(出口氏)。

野村氏は、「AL32」ですべての信号がアップコンバートされるなら、基本的には2系統のクロックは必要ないのでは? と素朴な疑問も投げた。それに対して出口氏は「そもそも『AL32』の動作にもマスタークロックが必要となるのです。ちなみに、『AL32』をつかさどるFPGAに提供されるクロックは、たとえ位相がズレたとしても刻む間隔が正しければ問題ありません。だからこそFPGAの近くではなく、DAC近傍にクロックを配置しているのです」と説明していた。

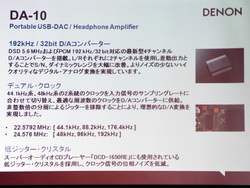

また、DA-10が32ビットのDACを採用しているのは、「AL32」でアップコンバートされた信号をそのまま入力して処理するためという理由もあるのだという。出口氏はこの32ビットDACに「PCM1795」を採用していることにも触れ、下記のようにコメントしていた。

「PCM1795はSACDプレーヤーのDCD-1650REから採用していますが、DACの中では純粋にD/A変換だけを行っていて、先ほど説明した通り内蔵のデジタルフィルターはパスしています。こういう使い方が可能なDACはそう多くありません。また、PCM1795はパワフルな音質で、低位相雑音という面でも強みがあります。DCD-SX1でその使いこなし方を手中にしたことで、DA-300USB、そしてDA-10にも採用するに至りました」(出口氏)

デジタル部のもうひとつの大きな特徴といえる「DAC Master Clock Design」にも話は及んだ。DA-10はDACをマスターとして周辺回路にクロックを供給することで、デジタル回路の高精度な同期を実現する。そして、DACに供給するクロックの精度を最優先するために、DAC近傍にクロックモジュールを配置しているのだ。

「マスタークロックの置く場所をDACの近傍とした理由は、各デジタル部の中でも特にDACが、精度の高いマスタークロックを必要としているからです。どれだけ高性能なDACでも動作する基準はクロックです。ですから高品位なクロックを用意してあげれば、そのDACの最高のパフォーマスが得られます。そのために、DACの近傍にクロックを配置しているのです」(出口氏)

また、44.1kHz系と48kHz系で2系統のクロックを用意している点についても説明してくれた。「なぜクロックが2つあるのかというと、44.1kHz系のクロックで48kHz系に合わせようとしても定数倍にならないので、忠実なクロック生成が難しく、時間軸上の揺らぎ(ジッター)が出やすくなってしまいます。ジッターは音質にもろに影響してまうので、クロックを2系統配置して音源ごとに純度の高いクロックを提供してジッターを防いでいるのです」(出口氏)。

野村氏は、「AL32」ですべての信号がアップコンバートされるなら、基本的には2系統のクロックは必要ないのでは? と素朴な疑問も投げた。それに対して出口氏は「そもそも『AL32』の動作にもマスタークロックが必要となるのです。ちなみに、『AL32』をつかさどるFPGAに提供されるクロックは、たとえ位相がズレたとしても刻む間隔が正しければ問題ありません。だからこそFPGAの近くではなく、DAC近傍にクロックを配置しているのです」と説明していた。

また、DA-10が32ビットのDACを採用しているのは、「AL32」でアップコンバートされた信号をそのまま入力して処理するためという理由もあるのだという。出口氏はこの32ビットDACに「PCM1795」を採用していることにも触れ、下記のようにコメントしていた。

「PCM1795はSACDプレーヤーのDCD-1650REから採用していますが、DACの中では純粋にD/A変換だけを行っていて、先ほど説明した通り内蔵のデジタルフィルターはパスしています。こういう使い方が可能なDACはそう多くありません。また、PCM1795はパワフルな音質で、低位相雑音という面でも強みがあります。DCD-SX1でその使いこなし方を手中にしたことで、DA-300USB、そしてDA-10にも採用するに至りました」(出口氏)