映像再生機器用ロジック基板をコンパクトに実現

パナソニック、1チップでのHEVC 4K60p再生/HDMI出力に対応したLSIを開発

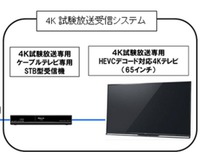

パナソニックは、HEVC規格の「Main10 Profile」に準拠し、新著作権保護に対応した映像再生を1チップで実現するシステムLSIを開発した。これにより、デジタルサイネージなどの大型ディスプレイ用に、濃淡が滑らかで動きの速い映像を再生させることが可能になる。量産出荷開始は2014年10月(時期応談)としている。

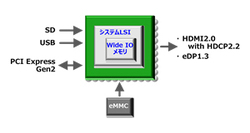

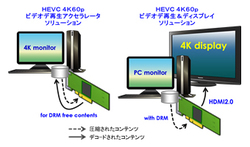

このLSIは、1チップでHEVC規格により圧縮された4K60p、10ビットカラー映像をリアルタイムにデコードして再生することができるため、滑らかな濃淡を表現した映像を出力するデジタルサイネージなどの実現が可能となるとのこと。また、このLSIは複雑な基板設計が必要となる外付けDDRメモリーを使用せずに設計ができるため、基板をコンパクトにすることが可能で、映像再生機器への組込みが容易になる。

新著作権保護「HDCP2.2」に対応した出画インターフェース「HDMI2.0」により、様々な映像を多様な表示機器に出力できる。

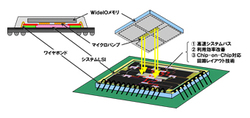

また、メモリーチップとの1パッケージ化により、外付けDDRメモリーを不要とするシステムが構築でき、コンパクトで低電力なロジック基板が実現できる。PCI Expressにも対応しているため、パソコン用PCIアドインカードとして実装することでパソコンの動画再生機能を拡張して、4K映像再生をすることも可能だ。

こうした高精細映像の処理は、同社の従来品比で2倍の処理性能を実現した、HEVCハードウェアデコーダ回路設計技術が実現している。4K60p対応の各種高速ビデオインターフェース技術、新著作権保護技術「JEDEC(Joint Electron Engineering Council)」準拠のWide IOメモリーを高効率にアクセスできる独自のバス・メモリアーキテクチャ、チップ・オン・チップ実装のためのチップレイアウト技術、PCI Expressインターフェース上のリアルタイム映像伝送技術なども、このLSIの実現に貢献している

同社によれば、映像の4K化によるデータ量の増加に伴い、効率的な画像圧縮/再生技術が求められているとのこと。HEVCで圧縮された4K画像の再生用LSIはすでにあるものの、コンパクトで低電力なHEVC対応システムを実現できる高速な外付けメモリーの内蔵化や新著作権保護に対応した映像出力LSIが求められていた。

なお本製品は、2014年6月11日〜13日に幕張メッセで開催される「デジタルサイネージジャパン2014」に出展される。

このLSIは、1チップでHEVC規格により圧縮された4K60p、10ビットカラー映像をリアルタイムにデコードして再生することができるため、滑らかな濃淡を表現した映像を出力するデジタルサイネージなどの実現が可能となるとのこと。また、このLSIは複雑な基板設計が必要となる外付けDDRメモリーを使用せずに設計ができるため、基板をコンパクトにすることが可能で、映像再生機器への組込みが容易になる。

新著作権保護「HDCP2.2」に対応した出画インターフェース「HDMI2.0」により、様々な映像を多様な表示機器に出力できる。

また、メモリーチップとの1パッケージ化により、外付けDDRメモリーを不要とするシステムが構築でき、コンパクトで低電力なロジック基板が実現できる。PCI Expressにも対応しているため、パソコン用PCIアドインカードとして実装することでパソコンの動画再生機能を拡張して、4K映像再生をすることも可能だ。

こうした高精細映像の処理は、同社の従来品比で2倍の処理性能を実現した、HEVCハードウェアデコーダ回路設計技術が実現している。4K60p対応の各種高速ビデオインターフェース技術、新著作権保護技術「JEDEC(Joint Electron Engineering Council)」準拠のWide IOメモリーを高効率にアクセスできる独自のバス・メモリアーキテクチャ、チップ・オン・チップ実装のためのチップレイアウト技術、PCI Expressインターフェース上のリアルタイム映像伝送技術なども、このLSIの実現に貢献している

同社によれば、映像の4K化によるデータ量の増加に伴い、効率的な画像圧縮/再生技術が求められているとのこと。HEVCで圧縮された4K画像の再生用LSIはすでにあるものの、コンパクトで低電力なHEVC対応システムを実現できる高速な外付けメモリーの内蔵化や新著作権保護に対応した映像出力LSIが求められていた。

なお本製品は、2014年6月11日〜13日に幕張メッセで開催される「デジタルサイネージジャパン2014」に出展される。